# Journal of Vibration Engineering

ISSN:1004-4523

Registered

**SCOPUS**

DIGITAL OBJECT IDENTIFIER (DOI)

**GOOGLE SCHOLAR**

**IMPACT FACTOR 6.1**

## Journal of Vibration Engineering (1004-4523) | Volume 24 Issue 7 2024 | www.jove.science Design of PD-PWM Based Asymmetrical 15-Level

### ReducedSwitchMultilevelInverterfor PVApplications

K.HARINATHREDDY<sup>1</sup>,S.LIKHITHA<sup>2</sup>,K.KRISHNAPRIYA<sup>3</sup>, N.CHINNAASWATH<sup>4</sup>,A.LOKESHREDDY<sup>5</sup>

<sup>1</sup>Assistant professor, Department of Electrical and Electronics Engineering, Annamacharya Institute of Technology and Sciences (AITS),Rajampet.

${}^{2,3,4,5} Student of Electrical Engineering, Annama charya Institute of Technology and Sciences (AITS), Rajampet.$

**ABSTRACT**: This paperpresents anewsingle-phase, 15-levelinverter for solar photovoltaic (PV) applications. It features fewer components and can be used to boost the output voltage of the solar PV modules from the MPPT to the maximum level. It is tested using the dSPACERTII 104 controller and the software packages Simulinkand MATLAB. The results of the study demonstrate that the proposed evice can perform well under different load conditions.

keywords: Solarphotovoltaic (PV) inverter, MPPT, converter, total harmonic distortion (THD).

#### 1.INTRODUCTION

Because of the vast usage of the fossil fuels, there is a sharp decrement in theavailability of fossil fuel resources. To meet the day-to-dayrequirementsofelectricity, it stimetoshifttotherenewableenergy sources. With the advancements in solar energy, the control techniques of grid connected inverters has been deploying from the few years. In order to obtain the above mentioned features, a multilevel inverter with minimum number of switches can be implemented to get a smooth sine wave. MLI's is widely used in high power applications such as large induction drive, UPS systems and FACTS systems.

Required output will be obtained from several level ofdc links that are used in the circuit .Most commonly there are three differenttypes of multilevel inverter topologies [1]-[2] used and they are Diode-clamped MLI's, Flying capacitor MLI's and Cascaded H-BridgeMLI's. Basically, three control techniques are available for controlling the grid connected multilevel inverters and those are Carrier wavecomparison technique, Hysteresis loop control technique and predictive control technique. The widely used technique is the carrier wavecomparison control, which tracks the output current by using a PI Controller [3]. But, it fails in reducing the steady-state error between thetarget current and the original current. The simplest control technique is the hysteresis loop control technique and it has the advantage ofhaving good robustness [4]-[6], but it has high ripple content in the output current, which may increase the losses and thereby reducing theefficiency of the system. The another major drawback is the unstable switching frequency. Model Predictive control is the main branch of Predictive control techniques. A model has to be established for the system in MPC [7]-[12]. Depending upon the designed model, theupcoming values of the variables can be predicted. Based on the comparison of the predicted values and the required reference values,

taken.MPCstructureisverysimplefordesigningandmodelling.Predictivecontrolmodecanbeimplementedonadigitalsignal processorand itsoutputhassmall distortionsin the currentandharmonicsareminimized.

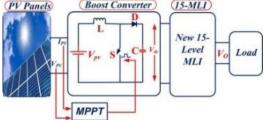

FIGURE1. Proposed system configuration.

#### 1.CONFIGURATIONOFPROPOSEDSYSTEMS

Figure 1 depicts the proposedSolarPV Arrays-basedconverter boost converterwithanintegratedinverter. Cascadedor parallelphotovoltaic cells must be connected based on whether higher voltage or current is required. They are built to last and can withstand theharshest environmental conditions. This Solar PV cell design is accomplished by simulating natural environmental conditions, which arethen processed to produce the Irradiance vs Time graph and the Temperature vs Time graph, both of which have been simulated for tenseconds. A solar cell can be represented as a current source connected in parallel to a diode, with the output of the current source beingdirectly proportional to the amount of light falling on the cell. The diode thus defines the VI characteristics of the cell. It cannot use thismodel to simulate reality because it lacks other external factors besides sunlight. These, however, can be solved by increasing complexityand accuracy. The diodes are then connected in parallel with two distinct sets of saturation current. Consider the temperature dependence of the diode and its saturation current connected with a series of resistances in this programme.

#### Journal of Vibration Engineering(1004-4523) | Volume 24 Issue 7 2024 | www.jove.science

The quality of the output of a power-producing device is determined by its ability match the curve. This is because, unlike other facilities, renewable sources can't be easily controlled. They have various external factors that can affect the output, which is why algorithms

are developed to ensure that the power supply is always regulated. This case involves the implementation of a modified version of the algorithm known as the maximum power point tracking. This electronic boost converter is used in combination with a solar cell array to provide the best possible power output. This model was chosen to study the scope of work and the various aspects of a project in the context of the development of a tracking algorithm for real-time radiation therapy. It takes into account the various peak power points of the system and compares them to the strategies and configurations that can be used to achieve the best possible results. The conventional DC to DC converter is necessary because the voltage generated by renewable sources is extremely low and difficult to regulate. As a result, these converters assist the system in reaching the required voltage level for long-term practical operation. C and L are the names given to the capacitor and inductor with values of 3.2nFand 94.22uH, respectively.

Itactsasa Jacquinal of eVibration ternstina (1904) system small of the converted of the con

Vpv

mandinfinitevalues. After 0.019 seconds, the boost voltage of the converter, which is 400 volts, is generated. Vo= (1-D)(1)

The course of orthogona advector more above the property of the p

The sources for the proposed system are taken into account by the PV simulator 5kW&8A. The converter simulation and experimental results are displayed in Figures 3–4 for solar PV. Increased DC-linking voltage from solar PV is possible with the boost converter. The obtained DC-linkvoltage can be fed into the proposed inverter, which will generate an AC stepped waveform.

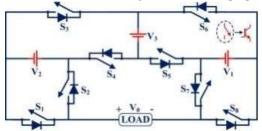

FIGURE5. Proposed topology of 15 levels.

TABLE2.Switchingstatesfor15L-MLI

| 1  | S2, S3, S5, S7 |

|----|----------------|

| 2  | S2, S3, S5, S8 |

| 3  | S1, S3, S7, S5 |

| 4  | S1, S3, S5, S8 |

| 5  | S2, S3, S6, S7 |

| 6  | S2, S3, S6, S8 |

| 7  | S1, S3, S6, S7 |

| 8  | S2, S4, S5, S7 |

| 9  | S2, S4, S5, S8 |

| 10 | S1, S4, S5, S7 |

| 11 | S1, S4, S5, S8 |

| 12 | S2, S4, S6, S7 |

| 13 | S2, S4, S6, S8 |

| 14 | S1, S4, S6, S7 |

| 15 | S1, S4, S6, S8 |

#### 1. PROPOSED15-LEVELMLI

Anew15-levelinvertershowninFigure5isbasedonaboostconverter'sDC-linkvoltage.ItfeatureseightswitchesandthreeDC-sources.The design of the proposed inverter takes into account the strategy of keeping short circuits out of the path of current. The initial level canbe achieved by switching the switches S2, 3, S5, S7, and S8 in a closed path. The total voltage of the system is calculated by taking intoaccount the blocking voltage of the switches. In the second mode, the switches S8, S2, and S3 are conduction. These are chosen to avoidshortcircuits,andeventhesumofthelowertheblockingvoltagesofasemiconductorswitch,theloweritscost-

effectivenessandtheTSV. Table I shows the selection patterns of switches up to 15 levels, and these are chosen based on the conditions. The overall loop of the switch conduction helps in reducing the voltage across the switches and improving the efficiency of an inverter.

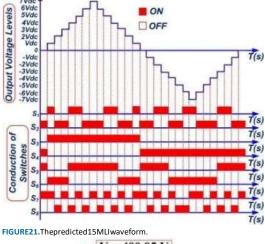

Inordertogenerate15levelsofoutputvoltage,aninverterisproposedwithasymmetricalDCinputsourcesina1:2:5ratio.Sourcevoltagesare taken as Vdc = V1 = 57.15V, V2 = 114.3V, and V3 = 285.75V, respectively, as shown in Table 2. Gate pulses are generated using thestaircasePWMtechnique.Inmode1,thenumberofV2+V3switchesthatareONwhiletheotherswitchesareOFFdeterminestheoutputvoltage.

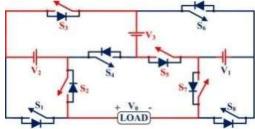

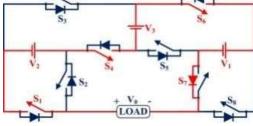

FIGURE6.Case-1forthe15MLI

METSZETJOURNAL ISSN:2061-2710

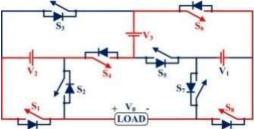

FIGURE7.Case-2forthe15MLI.

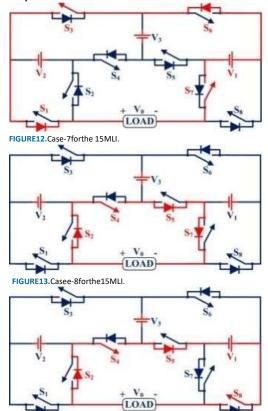

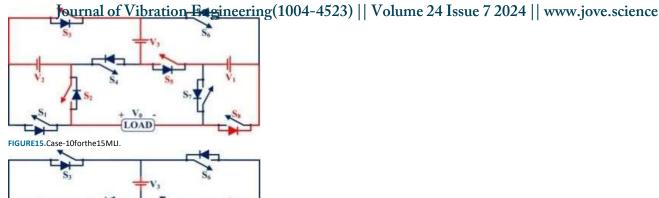

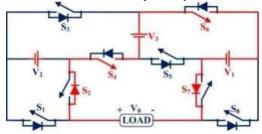

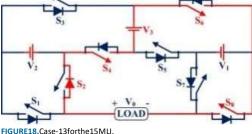

The output voltage in mode-2 is V1 + V2 + V3, the S2, S3, S5, S8, and S9 switches are ON, and the remaining switches are OFF. Inmode-3,theS1,S3,S7,andS5switchesareON,whiletheremainingswitchesareOFF,andtheoutputvoltageisV3.Inmode-4,theoutputvoltage the number of V1 + V3, the S1, S3, S5, and S8 switches are turned on, and the remaining switches are turned off. In mode-5, theoutput voltage equals V1 + V2, the S2, S3, S6, S7 switches are turned on, and the remaining switches are turned off. The output voltage of the S2 and S3 switches is equal to V2. The other switches are turned on and off. In mode 6, the output voltage of the S6 and S8 switches isequalto V2.In mode7, the output voltage of the S1 and S3 switches is equal to V1. The remaining switchesarealsoturnedon.Inmode8,theoutputvoltageoftheS2andS4switchesisON,whiletheotherswitchesareoff.TheS2,S4,S5,S8andotherswit chesareONinmode9, while the others are off. In mode 10, the S1, S4, S5, S7 and other switches are ON, while the others are off. In mode the S1, S4, S5,S8andotherswitchesareON,whiletheothersareoff.Theoutputvoltageis -(-V1+V3)inmode-12, with the S2, S4, S6, S7 switches ON and the remaining switches OFF. In mode-13, the S2, S4, S6, S8, and S10 switches will be ON, while the remaining switches will be OFF; the output voltage is -V3. The output voltage is - (-V1+V2+V3) in mode-14, with the S1, S4, S6, S7 switches ON and the remaining switchesOFF. In mode-15, the S1, S4, S6, and S8 switches are turned on, while the remaining switches are off, and the output voltage is -(V2 + V3). AlloperationalmodesaredepictedinFig.6 toFig.21based onthe conduction of switches and the expected waveform.

#### A. CIRCUITPARAMETERSDESIGN

The oversimplified question naires below can be used to calculate the suggested inverter circuit parameters, such as the number of levels (NL), number of switches (NSW), number of DC sources (NSDC), and peak output voltage (VOP).

NSDC = n (2)

$NSW = (2nk1+1)+(2nk2+1) + \dots + (2nkj+1)(3)$

NL=(2nk1+1-1)+(2nk2+1-1)...+(2nkj+1-1) (4)

$VOP = ((2nk1+1-2)/2 + (2nk2+1-2)/2 + .... + (2nkj+1-2)/2) \times Vdc$  (5)

Wheren and k represent the proposed inverter's sources and modules, respectively. Equations (2), (3), (4), and (5) are solved for theparameters with n=3 and

**METSZETJOURNAL** ISSN:2061-2710

FIGURE16.Case-11forthe15MLI.

k=1 and  $V_{dc} = V_1 = 57.15$  V, respectively. The  $N_{SDC} = 3$ ,  $N_{SW} = (2^{3+1}) = 8$ ,  $N_L = (2^{3+1} - 1) = 15$ , and

FIGURE17.Case-12forthe15MLI.

FIGURE18. Case-13 for the 15 MLI.

FIGURE19. Casee-14 for the 15 MLI.

FIGURE20. Casee-15 for the 15 MLI.

$V_{OP} = \left(\frac{2^{3+1}-2}{2}\right)*57.15 = 400, \\ 05V. The proposed inverter was implemented using two basic modules (k=2) to generate a 29-output voltage level.$

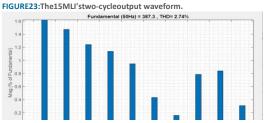

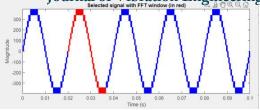

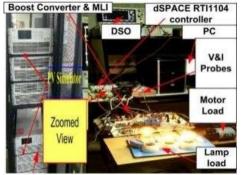

Using MATLAB/S imulink simulation and the dSPACERTI11014 Controller for experimental validation, the suggested inverter was verified as should be a suggested of the controller for experimental validation and the dSPACERTI11014 Controller for experimental validation, the suggested inverter was verified as should be a suggested of the controller for experimental validation and the dSPACERTI11014 Controller for experimental validatwn in Fig. 34. The output wave forms and THD of the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the figures 22-27 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the figures 22-27 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed in Figures 22-27. The high power CM75DU-100 and the simulation are displayed as a simulation are displayed and the simulation are displayed as a simulation are displayed

**METSZETJOURNAL** ISSN:2061-2710

12HIGB TOWEROOD & VIALATION - Engineering (110) And 523h He Volume 24k Volume 27c2024 The USPAC jover policy controlled the co e pulsesby employingtheTLP250driver techniqueof the staircasePWM.

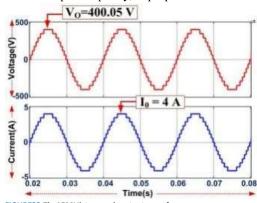

FIGURE22. The 15 MLI's single-cycle output wave form.

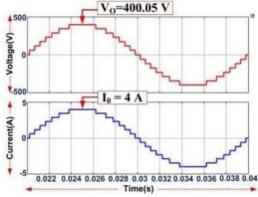

Single-phase loads with a resistance of 100 ohms, 175 mh, and 0.5 HP and a power factor of 0.75 were utilized for the simulation and experiment, respectively. The source voltages used are Vdc = V1 = 57.15V, V2 = 114.3V, and V3 = 285.75V in order to obtain the maximumpeak outputvoltageVo=400.05V.The robustnessoftheproposed 15-level inverter isanalysed with linear and non-linearloads.

As per Figs. 28 and 29, the experimentally obtained output power, output voltage, and output current for the proposed inverter withlinearloads are Po=782.55W, Vo=400.05V,Io=4A,Vrms=277.5V,andIrms=2.82A.InFig. inverter's performance andeffectivenessareconfirmedwithamotorload(non-

linear)usingtheoutputvoltageandcurrent(Vo=400.05V,Io=6.5A).Thedynamicloadisusedtotestand incorporate swaps from linear to nonlinear. The suggested inverter achieves the maximum system peak output voltage of 400V andkeeps a stable output during dynamic load changes, as shown in Figs. 31 and 32. According to IEEE standards, the efficiency is 95.237%, and theexperimental THD is 4.41%. Toenhancepower quality, the proposed inverter can be linked to the grid and FACTS.

${\small \begin{array}{c} {\tt METSZETJOURNAL}\\ {\tt FIGURE24.The T15MLITHD Simulation Engineering (1004-4523) \mid\mid Volume~24~Issue~7~2024 \mid\mid www.jove.science \end{array}}$

METSZETJOURNAL ISSN:2061-2710

#### Journal of Vibration Engineering (1004-4523) | Volume 24 Issue 7 2024 | www.jove.science

FIGURE25. Waveform of the 15 MLI experiment

FIGURE26.Prototypemodelof15MLI.

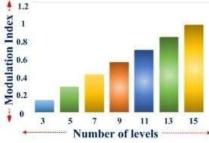

TABLE3.Levels vsModulationindex

| MI (Modulation Index) | L (Number of Levels) |

|-----------------------|----------------------|

| 0.14                  | 3                    |

| 0.29                  | 5                    |

| 0.43                  | 7                    |

| 0.57                  | 9                    |

| 0.71                  | 11                   |

| 0.86                  | 13                   |

| 1.00                  | 15                   |

FIGURE27.Levels vsMlof15MLI.

#### 1. CONCLUSION

Thispaperproposes an ewtype of 15-levelin verter for use in solar PV systems. It uses a boost converter to generate an AC output voltage. The proposed inverter has fewer components and low total harmonic distortion. A proposed inverter uses eight insulated-gating bipolar transistors, which are triggered by a pulse-

widthmeasurementtechniqueknownasthestaircasemodulationtechnique. Ithashighefficiency, lowerlosses, and low harmonic distortion. Compar edtomultile velmodels, this design of fressignificant reduction in complexity and stress. The design of the proposed inverter was tested with different types of load conditions, such as non-linear and linear loads. It was able to maintain stable performance under dynamic conditions, which makes it suitable for applications.

#### REFERENCE

- [1]M. D. Siddique, S. Mekhilef, N. M. Shah, A. Sarwar, A. Iqbal, and M. A. Memon, "A new multilevel inverter topology with reduces witch count," *IEEE Access*, vol. 7,pp.58584–58594,2019.

- [2].A. Salem, H. Van Khang, K. G. Robbersmyr, M. Norambuena and J. Rodriguez, "Voltage Source Multilevel Inverters With ReducedDeviceCount:TopologicalReviewandNovelComparativeFactors", inIEEETransactionsonPowerElectronics,vol.36,no.3,pp.2720-2747,March2021.

- [3].A. Poorfakhraei, M. Narimani and A. Emadi, "A Review of Modulation and Control Techniques for Multilevel Inverters in TractionApplications", inIEEE Access, vol. 9,pp.24187-24204,2021.

- [4].C. Dhanamjayulu, D. Prasad, S. Padmanaban, P. K. Maroti, J. B. Holm-Nielsen, and F. Blaabjerg, "Design and implementation ofseventeen level inverter with reducedcomponents," IEEE Access, vol.9, pp.16746-16760, 2021.

- [5].Niviya Varghese, Rabiya Rasheed, "Design of a New Five Level MLM based Multilevel Inverter", 2020 IEEE International Powerand Renewable Energy Conference, pp.1-6,2020.

- [6].M. K. Das, A. Sinha and K. C. Jana, "Hybrid Multilevel Inverter with Reduced Switches Topology," 2018 5th IEEE Uttar PradeshSection InternationalConferenceonElectrical, ElectronicsandComputerEngineering(UPCON)

- [7]. P. Omer, J. Kumar and B. S. Surjan, "A New Multilevel Inverter Topology with Reduced Switch Count and Device Stress," 20185th IEEEUttar PradeshSection International ConferenceonElectrical, ElectronicsandComputer Engineering (UPCON)

- [8].P. R. Bana, K. P. Panda, R. T. Naayagi, P. Siano and G. Panda, "Recently Developed Reduced Switch Multilevel Inverter

METSZETJOURNAL ISSN:2061-2710

[9]. H. LOUIDIA RENTANTION Engineering (Julian, "4523) Reduceds unch 24 Louis 17 2024 for PWAPP LIQUED 1th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC).

[10]. V.S.P.K, S. Peddapatiand S. V.K. Naresh, "A Single Phase Seven-level MLI with Reduced Number of Switches Employing a PVFed SIMO DC-DCC onverter," 2020 IEEE Students Conference on Engineering & Systems (SCES).

METSZETJOURNAL ISSN:2061-2710

Journal of Vibration Engineering(1004-4523) | Volume 24 Issue 7 2024 | www.jove.science